# CS32G020/1 Datasheet

Two-channel USB Type-C PD controller

V/1 0

### 1. Product Overview

### 1.1. Functional Features

### Type-C and USB PD supports

- Supporting USB PD3.1 and PPS.

- Certified by USBIF, TID: 1047

- Configurable RP and RD at CC port.

- Supporting 2 Type-C ports, and allowing independent PD communication.

- The CC port supports 21V voltage resistance.

- Integrated with 2 high-voltage control ports.

- Supporting fast role swap (FRS).

### Other protocols

- Supporting QC4.0+, SCP, FCP and AFC protocols.

- Supporting VOOC protocol.

- Supporting BC1.2 and Apple 2.4A.

- Supporting all configuration on DP and DM.

- Supporting multiple quick charge protocol input such as FCP and AFC.

### **Peripherals**

- Max. 27 universal (GPIO) pins

- 3 × 16-bit timers, 8-bit prescaler

- 1 set of UART

- 1 set of SPI

- 1 set of I<sup>2</sup>C (supporting master/slave mode)

- 2 analog comparators

- 12 bit Analog-to-digital convertor (ADC)

- 11-bit digital-to-analog convertor (DAC)

- Undervoltage detection (BOD)

### 32-bit MCU

- An ARM®Cortex<sup>TM</sup>-M0 core, with max. clock rate of 48 MHz

- 60K Flash memory for storing applications (APROM)

- Configurable data Flash (Data Flash)

- 4KB startup code space (LDROM)

- Built-in 8KB SRAM

- System startup section configurable from APROM, LDROM or SRAM

#### Clock and crystal oscillator

- 24/8 MHz built-in oscillator (HSI) (25°C, 5V, 1% error)

- 10 KHz built-in low power oscillator (LSI)

# Operating modes (low power mode, multi-clock low power strategy)

- Normal mode, operating current is 10 mA@5V, 25°C

- Sleep mode, operating current is 2 mA@5V, 25°C

- Deep-Sleep1 mode, operating current is 100 μA@5V, 25°C

- Deep-Sleep2 mode, operating current is 12 μA@5V, 25°C

- Deep Power-Down mode, operating current is 2.5 μA@5V, 25°C

#### Chip safety

- Providing multilevel confidential policies for Flash memory.

- Providing CRC-32 computing element with polynomial as 0x4C11DB7 (same as Ethernet standard).

- Integrating SRAM to support odd/even parity.

- Operating conditions:

- --Operating temperature: -40°C~85°C

- --Operating voltage: 2.5 V~5.5 V

#### **Package**

- QFN24

- OFN32

### **Application scope**

- Adapter

- Power banks

- Car chargers

- HUB

- Display

### 1.2. Product description

The CS32G020/1 Series are USB Type-C and USB PD controllers suitable for device or power supply applications. The series integrate two-channel independent Type-C CC and USB PD features, Load Switch Driver and USB BC1.2. Moreover, the series support fast charging protocols of multiple cell phone models to strengthen the charging compatibility of end devices. The series are applicable to adapters, power banks, car chargers, HUB and displays. One chip can easily provide a solution with two Type-C ports.

### 1.3. Model selection table

Table 1 CS32G020/1 series

| Model        | Flash | SRAM | Ю  | CC<br>port  | PD<br>Module | Dead<br>batteries<br>function | QC<br>PHY  | Timer   | ADC            | DAC   | Package |

|--------------|-------|------|----|-------------|--------------|-------------------------------|------------|---------|----------------|-------|---------|

| CS32G020K8U6 | 64K   | 8K   | 27 | 2<br>groups | 2            | Support                       | 2 channels | 3*16bit | 24-<br>channel | 11bit | QFN32   |

| CS32G020E8U6 | 64K   | 8K   | 19 | 2<br>groups | 2            | Not supported                 | 2 channels | 3*16bit | 20-<br>channel | 11bit | QFN24   |

| CS32G021K8U6 | 64K   | 8K   | 27 | 2<br>groups | 2            | Support                       | 2 channels | 3*16bit | 24-<br>channel | 11bit | QFN32   |

| CS32G021E8U6 | 64K   | 8K   | 19 | 2<br>groups | 2            | Not supported                 | 2 channels | 3*16bit | 20-<br>channel | 11bit | QFN24   |

# 1.4. Block diagram

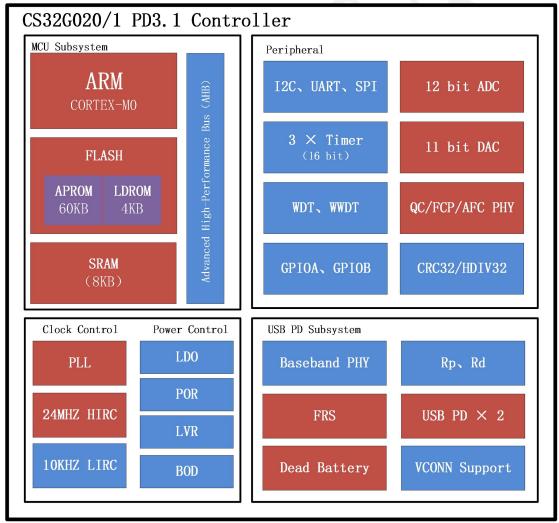

### 1.4.1. Block diagram of function modules

Figure 1 Block diagram of CS32G020/1 system

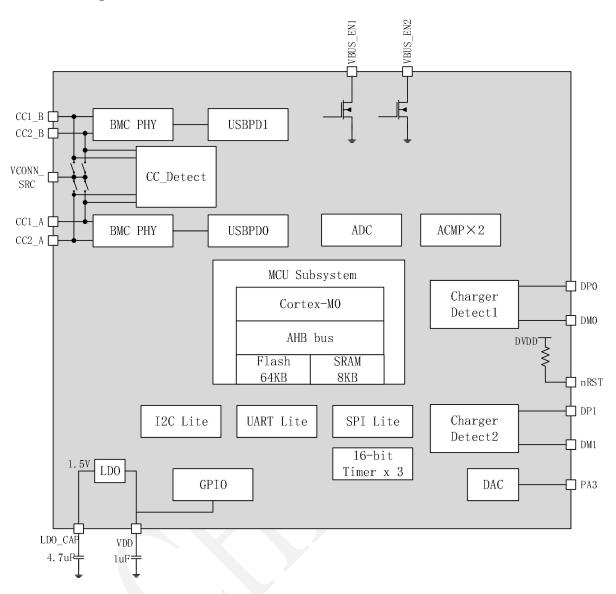

### 1.4.2. Block diagram of internal circuit

Figure 2 Block diagram of internal circuit

# **Table of Contents**

| 1. Product Overview                      |        |                                      |

|------------------------------------------|--------|--------------------------------------|

| 1.1. Functional Features                 |        | 1                                    |

| 1.2. Product description                 |        | 1                                    |

| 1.3. Model selection table               |        | 2                                    |

| 1.4. Block diagram                       |        | 2                                    |

| 1.4.1. Block diagram of function module  | S      | 2                                    |

| 1.4.2. Block diagram of internal circuit |        | 3                                    |

| Version History                          |        |                                      |

| 2. Definitions of pins                   | •••••  | 8                                    |

| 2.1. QFN24                               |        | 8                                    |

| 2.2. QFN32                               |        | 9                                    |

| 2.3. Descriptions of pins                |        | 10                                   |

| 3. Functional Description                |        |                                      |

| 3.1. MCU subsystem                       |        | 14                                   |

| 3.2. Flash                               |        | 14                                   |

| 3.2.1. LDROM                             |        | 15                                   |

| 3.3. User configuration zone             |        | 15                                   |

| 3.4. Encrypted zone                      |        | 18                                   |

| 3.5. USB PD                              |        | 19                                   |

| 3.5.1. Type-C port                       |        | 19                                   |

| 3.5.2. USB PD physical layer             |        | 19                                   |

| 3.6. VBUS PFE control port               |        | 19                                   |

| 3.7. ADC                                 |        | 20                                   |

| 3.8. DAC                                 |        | 20                                   |

| 3.9. Analog comparator                   |        |                                      |

| 3.10. GPIO                               |        |                                      |

| 3.11. Communication interface            |        | 21                                   |

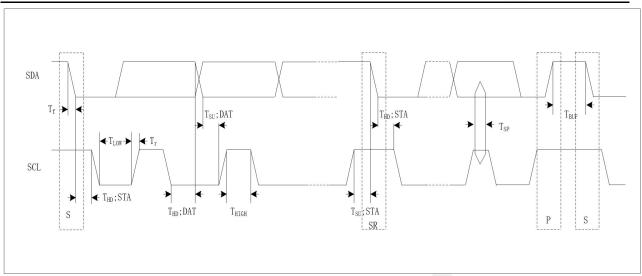

| 3.11.1. I <sup>2</sup> C                 |        | 21                                   |

| 3.11.2. SPI                              |        | 21                                   |

| 3.11.3. UART                             |        | 21                                   |

| 3.12. Timer                              |        | 21                                   |

| 3.13. Watch dog timer                    |        | 22                                   |

| 3.13.1. WDT                              |        |                                      |

| 3.13.2. WWDT                             |        | 22                                   |

| 3.13.3. WDT Lite                         |        | 22                                   |

| 3.14. Arithmetic unit                    |        | 22                                   |

| 3.14.1. Single-cycle multiplier          |        | 22                                   |

| 3.14.2. Hardware divider                 |        | 22                                   |

| 3.14.3. CRC32 computing element          |        | 23                                   |

| 3.15. Power management                   |        | 23                                   |

| 3.15.1. Normal Operation Mode            |        | 24                                   |

| 3.15.2. Sleep mode                       |        |                                      |

| www.chipsea.com                          | 4 / 47 | Chipsea Technologies (Shenzhen) Corp |

| 3.15.3. Deep-Sleep 1 Mode                                   | 24 |

|-------------------------------------------------------------|----|

| 3.15.4. Deep-Sleep 2 Mode                                   | 24 |

| 3.15.5. Deep Power-Down Mode                                | 24 |

| 4. Application programming                                  | 25 |

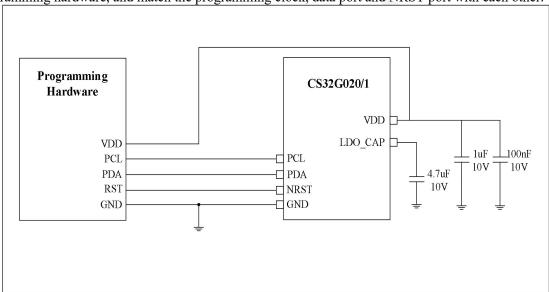

| 4.1. Flash programming through serial programming interface | 25 |

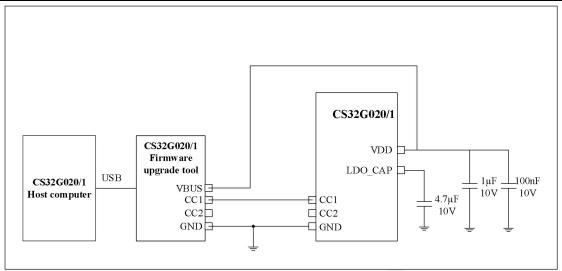

| 4.2. Updating applications through Type-C interface         |    |

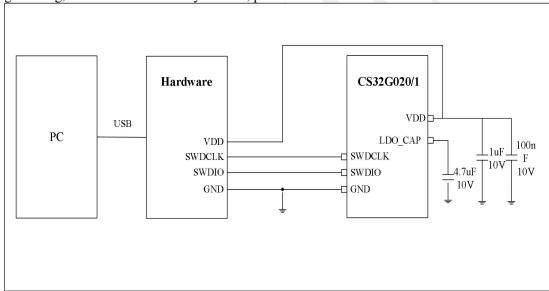

| 4.3. Programming through SWD interface                      |    |

| 4.4. Selection of programming method                        | 26 |

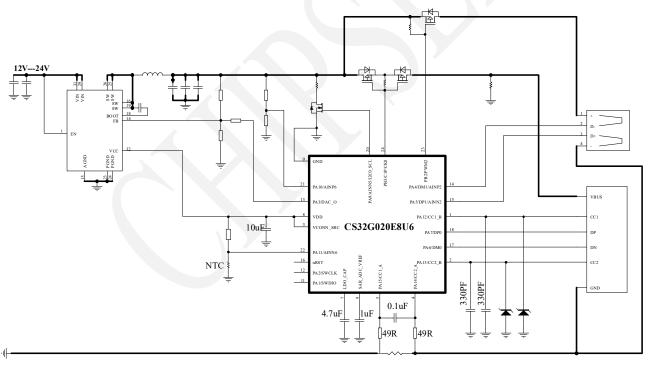

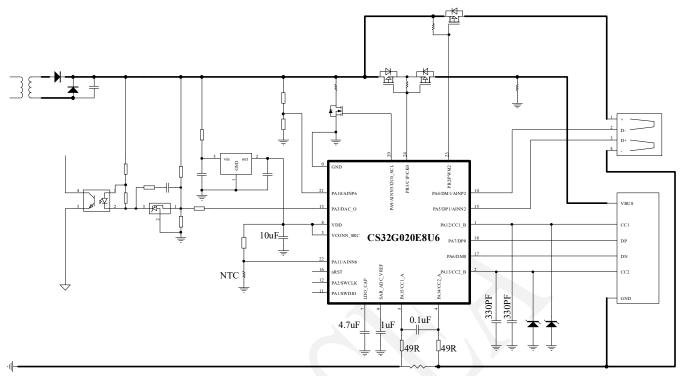

| 5. Typical application                                      | 27 |

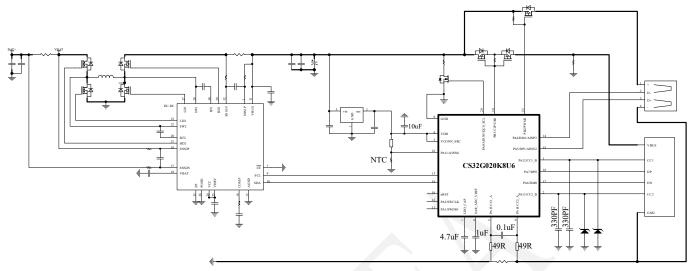

| 5.1. Power banks                                            | 27 |

| 5.2. Car chargers                                           |    |

| 5.3. AC adapters                                            |    |

| 6. Electrical characteristics                               | 29 |

| 6.1. Limit value                                            |    |

| 6.2. Electrical characteristics of DC power supplies        |    |

| 6.3. Electrical characteristics of AC power supplies        |    |

| 6.3.1. Internal 24/8 MHz RC Oscillator                      |    |

| 6.3.2. Internal 10 KHz RC Oscillator                        |    |

| 6.3.3. PLL characteristics.                                 |    |

| 6.3.4. I <sup>2</sup> C characteristics                     |    |

| 6.3.5. Characteristics of Flash                             | 33 |

| 6.4. Characteristics of analogs                             | 33 |

| 6.4.1. 12-bit ADC                                           | 33 |

| 6.4.2. 11-bit DAC                                           | 34 |

| 6.4.3. Comparators                                          |    |

| 6.4.4. Internal reference voltage                           | 35 |

| 6.4.5. Specifications of LDO and Power management           |    |

| 6.4.6. Low voltage reset                                    | 36 |

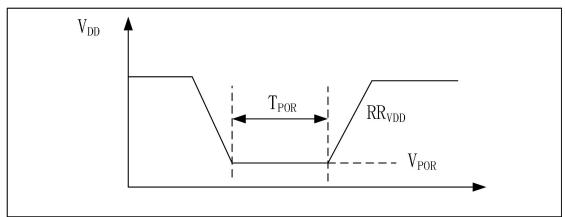

| 6.4.7. Power-on reset.                                      | 36 |

| 6.4.8. Characteristics of Type-C                            |    |

| 6.4.9. Characteristics of QC3.0                             | 37 |

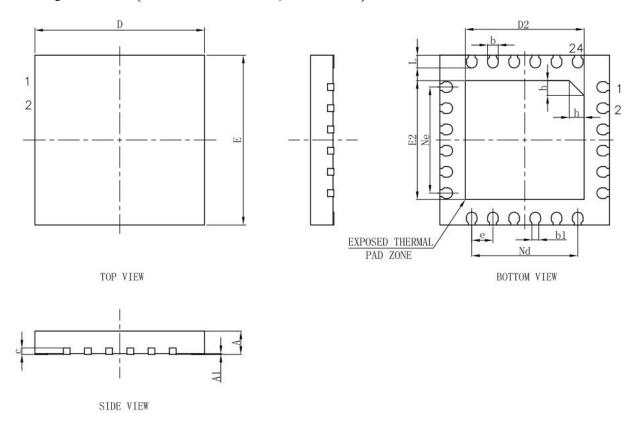

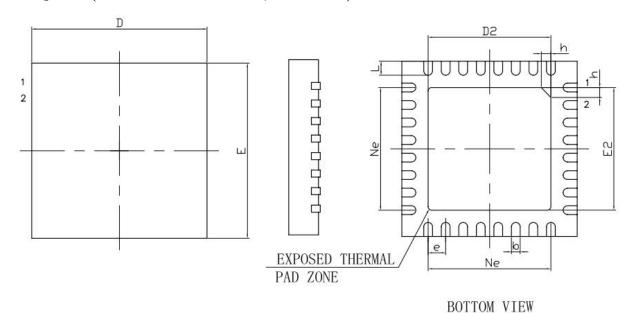

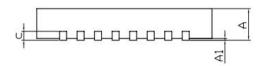

| 7. Package information                                      | 38 |

| 7.1. QFN24-PIN (4 mm * 4 mm * 0.55, e = 0.5 mm)             | 38 |

| 7.2. QFN32 (5 mm * 5 mm * 0.75 mm, e = 0.5 mm)              | 39 |

| 7.3. Thermal characteristics                                | 40 |

| 7.4. Humidity characteristics                               | 40 |

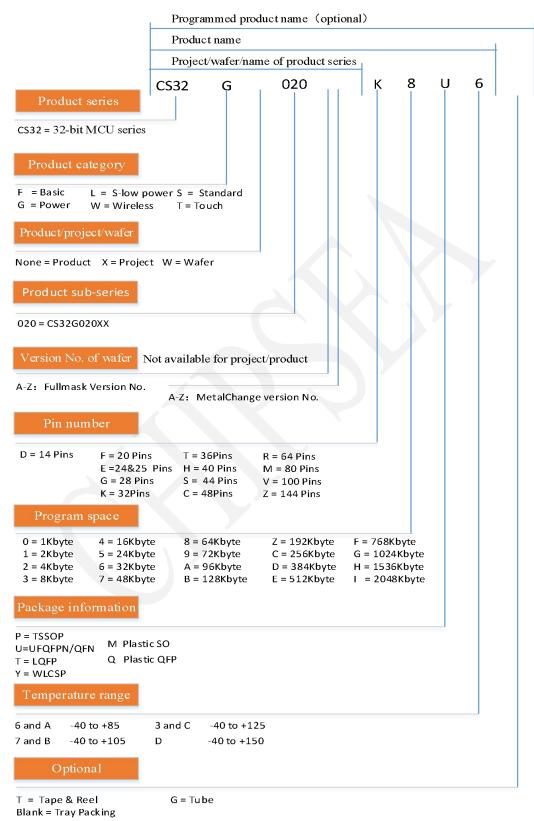

| 8. Naming conventions of products                           | 41 |

| 8.1. Description of product name                            | 41 |

| 8.2. Description of marks on product                        |    |

| 9. Order Information                                        | 43 |

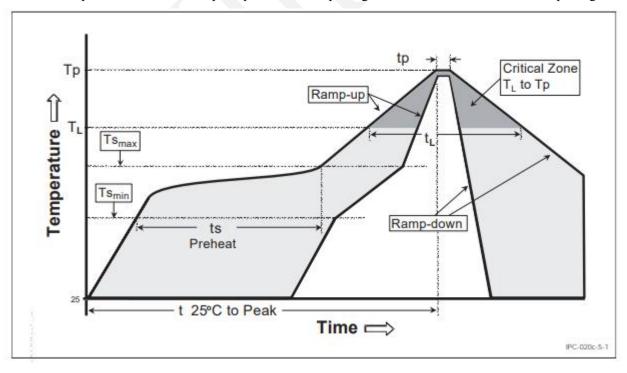

| 10. Reflow curve for reference, peak temperature            | 44 |

| 11. Package information                                     |    |

|                                                             |    |

| 12. HSF Statement | 47 |

|-------------------|----|

| 12.1. RoHS        | 47 |

| 12.2 DEACH        | 17 |

# **Version History**

| History version | Revised contents                                                                                                                                                                                 | Date       |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| V 1.0           | Initial version                                                                                                                                                                                  | 2018-05-05 |

| V 1.1           | <ol> <li>Add the user configuration zone, P15 - P18</li> <li>Add the description on encrypted zones, P18 - P19</li> </ol>                                                                        | 2018-09-03 |

| V 1.2           | Delete external crystal oscillators                                                                                                                                                              | 2018-10-24 |

| V 1.3           | <ol> <li>Add Chapter 9: Naming conventions of products</li> <li>Update the descriptions in Chapter 5</li> <li>Update resistance of RDM pull-down resistor in Characteristics of QC3.0</li> </ol> | 2019-02-13 |

| V 1.4           | <ol> <li>Modify DAC DNL, INL feature, P36</li> <li>Modify errors, P5, P15</li> <li>Modify QFN24 package information, P40</li> <li>Modify Encrypted zone for program mode, P20</li> </ol>         | 2019-04-02 |

| V 1.5           | <ol> <li>Modify QFN24 package information, P40</li> <li>Modify QFN32 package information, P41</li> <li>Add comparator response time, P37</li> <li>Modify typical application, P30</li> </ol>     | 2019-08-08 |

| V 1.6           | 1. Modify QFN24 package L value, P40                                                                                                                                                             | 2020-05-15 |

| V 1.7           | 1. Modify descriptions of pins of VCONN SRC in chapter 3.3                                                                                                                                       | 2021-02-19 |

| V 1.8           | 1. Update thermal characteristics of package QFN32                                                                                                                                               | 2021-09-29 |

| V 1.9           | 1. Update template and PD3.1                                                                                                                                                                     | 2022-09-07 |

# 2. Definitions of pins

## 2.1. QFN24

Figure 3 Diagram of pins: QFN24 (Top View)

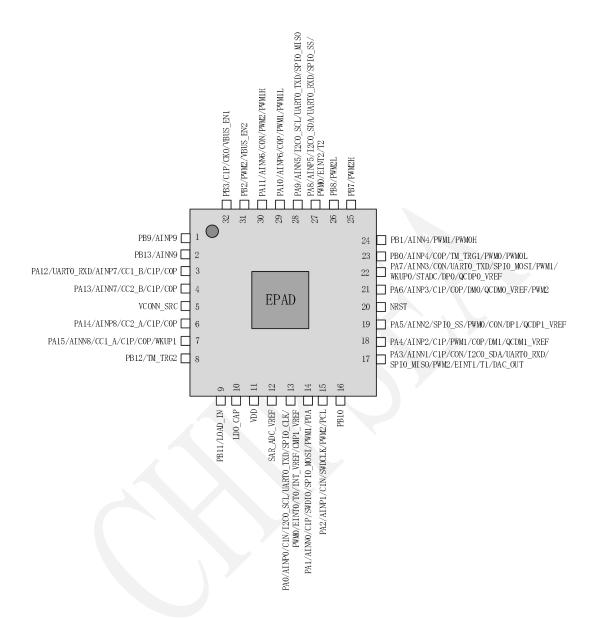

### 2.2. QFN32

Figure 4 Diagram of pins: QFN32 (Top View)

# 2.3. Descriptions of pins

Abbreviation of pin types

I: Digital input port

O: Digital output port

I/O: Digital input/output port

AI: Analog input port AO: Analog output port

P: Power supply

Table 2 Pin description

| QFN32<br>-PIN | QFN24<br>-PIN | Name of pin   | Type | Description                                                       |

|---------------|---------------|---------------|------|-------------------------------------------------------------------|

| 1             |               | PB9           | I/O  | Universal input/output pin                                        |

| 1             |               | AINP9         | AI   | AINP9 input                                                       |

| 2             |               | PB13          | I/O  | Universal input/output pin                                        |

| 2             |               | AINN9         | AI   | AINN9 input                                                       |

|               |               | PA12          | I/O  | Universal input/output pin                                        |

|               |               | UART0_RXD     | I    | UART0 receipt signal                                              |

| 3             | 1             | AINP7         | AI   | AINP7 input                                                       |

| 3             | 1             | CC1_B         | I/O  | End of USB PD1 CC1                                                |

|               |               | C1P           | AI   | Plus-end input of Comparator 1                                    |

|               |               | C0P           | AI   | Plus-end input of Comparator 0                                    |

|               |               | PA13          | I/O  | Universal input/output pin                                        |

|               |               | AINN7         | AI   | AINN7 input                                                       |

| 4             | 2             | CC2_B         | I/O  | End of USB PD1 CC2                                                |

|               |               | C1P           | AI   | Plus-end input of Comparator 1                                    |

|               |               | C0P           | AI   | Plus-end input of Comparator 0                                    |

|               | 3             |               | P    | VCONN power input end, requiring input voltage of                 |

| 5             |               | VCONN_SRC     |      | 2.5 V~5.5 V, VCONN voltage cannot be higher than                  |

|               |               |               |      | VDD+0.3V                                                          |

|               | 4             | PA14          | I/O  | Universal input/output pin                                        |

|               |               | AINP8         | AI   | AINP8 input                                                       |

| 6             |               | CC2_A         | I/O  | End of USB PD0 CC2                                                |

|               |               | C1P           | AI   | Plus-end input of Comparator 1                                    |

|               |               | C0P           | AI   | Plus-end input of Comparator 0                                    |

|               | 5             | PA15          | I/O  | Universal input/output pin                                        |

|               |               | AINN8         | AI   | AINN8 input                                                       |

|               |               | CC1_A         | I/O  | End of USB PD0 CC1                                                |

| 7             |               | C1P           | AI   | Plus-end input of Comparator 1                                    |

|               |               | C0P           | AI   | Plus-end input of Comparator 0                                    |

|               |               | WKUP1         | I    | Waking up pins under power down mode. Effective under high level. |

|               |               | PB12          | I/O  | Universal input/output pin                                        |

| 8             |               | TM TRG2       | I    | Timer External Trigger Input 2                                    |

|               |               | PB11          | I/O  | Universal input/output pin                                        |

| 9             | 6             |               |      | Universal input/ output pins, supporting 800K pull-               |

|               |               | LOAD_IN       | I    | down resistors                                                    |

| 1.0           |               | I DO CAD      | 1.0  | LDO output pin, requiring connection to a 4.7 μF                  |

| 10            | 7             | LDO_CAP       | AO   | capacitor                                                         |

| 11            | 8             | VDD           | P    | IO power (1.8 V~5.5 V)                                            |

| 12            | 9             | CAD ADC VIDEE | 40   | SAR_ADC voltage reference output, requiring                       |

| 12            | 9             | SAR_ADC_VREF  | AO   | connection to a 1 µF capacitor                                    |

| 12            | 10            | PA0           | I/O  | Universal input/output pin                                        |

| 13            | 10            | AINP0         | AI   | AINP0 input                                                       |

|     |     | C1N                                | AI                              | Minus-end input of Comparator 1                                                                                                                                         |

|-----|-----|------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |     | I2C0 SCL                           | I/O                             | I <sup>2</sup> C0 clock signal                                                                                                                                          |

|     |     | UARTO TXD                          | О                               | UART0 clock signal                                                                                                                                                      |

|     |     | SPI0 CLK                           | I/O                             | SPI0 clock signal                                                                                                                                                       |

|     |     | PWM0                               | О                               | PWM0 output                                                                                                                                                             |

|     |     | EINT0                              | I                               | EINT0 input                                                                                                                                                             |

|     |     | T0                                 | I                               | Timer 0 input                                                                                                                                                           |

|     |     | INT VREF                           | AO                              | Internal reference voltage output                                                                                                                                       |

|     |     | CMP1 VREF                          | AI                              | Voltage reference output of Comparator 1                                                                                                                                |

|     |     | PA1                                | I/O                             | Universal input/output pin                                                                                                                                              |

|     |     | AINN0                              | AI                              | AINNO input                                                                                                                                                             |

|     |     | C1P                                | AI                              | <u> </u>                                                                                                                                                                |

| 1.4 | 1.1 |                                    |                                 | Plus-end input of Comparator 1                                                                                                                                          |

| 14  | 11  | SWDIO                              | I/O                             | SWD data signals                                                                                                                                                        |

|     |     | SPI0_MOSI                          | I/O                             | SPI0 master output/slave input signals                                                                                                                                  |

|     |     | PWM1                               | 0                               | PWM1 output                                                                                                                                                             |

|     |     | PDA                                | I/O                             | Data port for programming                                                                                                                                               |

|     |     | PA2                                | I/O                             | Universal input/output pin                                                                                                                                              |

|     |     | AINP1                              | AI                              | AINP1 input                                                                                                                                                             |

| 15  | 12  | C1N                                | AI                              | Minus-end input of Comparator 1                                                                                                                                         |

| 13  | 12  | SWDCLK                             | I                               | SWD clock signal                                                                                                                                                        |

|     |     | PWM2                               | О                               | PWM2 output                                                                                                                                                             |

|     |     | PCL                                | I                               | Clock port for programming                                                                                                                                              |

| 16  |     | PB10                               | I/O                             | Universal input/output pin                                                                                                                                              |

|     |     | PA3                                | I/O                             | Universal input/output pin                                                                                                                                              |

|     | 13  | AINN1                              | AI                              | AINN1 input                                                                                                                                                             |

|     |     | C1P                                | AI                              | Plus-end input of Comparator 1                                                                                                                                          |

|     |     | C0N                                | AI                              | Minus-end input of Comparator 0                                                                                                                                         |

|     |     | I2C0 SDA                           | I/O                             | I <sup>2</sup> C0 data signals                                                                                                                                          |

| 17  |     | UARTO RXD                          | I                               | UART0 receipt signal                                                                                                                                                    |

|     |     | SPI0 MISO                          | I/O                             | SPI0 master input/slave output signals                                                                                                                                  |

|     |     | PWM2                               | 0                               | PWM2 output                                                                                                                                                             |

|     |     | EINT1                              | I                               | EINT1 input                                                                                                                                                             |

|     |     | T1                                 | I                               | Timer 1 input                                                                                                                                                           |

|     |     | DAC OUT                            | AO                              | DAC output                                                                                                                                                              |

|     |     | PA4                                | I/O                             | Universal input/output pin                                                                                                                                              |

|     |     | AINP2                              | AI                              | AINP2 input                                                                                                                                                             |

|     |     | C1P                                | AI                              | Plus-end input of Comparator 1                                                                                                                                          |

| 18  | 14  | COP                                | AI                              | Plus-end input of Comparator 0                                                                                                                                          |

| 10  | 14  |                                    | 0                               |                                                                                                                                                                         |

|     |     | PWM1                               |                                 | PWM1 output                                                                                                                                                             |

|     |     | DM1                                | AI                              | QC Port Group 1: minus-end input                                                                                                                                        |

|     |     | QCDM1_VREF                         | AO                              | QCDM1_VREF voltage output                                                                                                                                               |

|     |     | PA5                                | I/O                             | Universal input/output pin                                                                                                                                              |

|     |     | AINN2                              | AI                              | AINN2 input                                                                                                                                                             |

|     | 15  | C0N                                | AI                              | Minus-end input of Comparator 0                                                                                                                                         |

|     |     | CDIO CC                            | I/O                             | SPI0 chip select signals                                                                                                                                                |

| 19  | 15  | SPI0_SS                            |                                 | 1 0                                                                                                                                                                     |

| 19  | 15  | PWM0                               | О                               | PWM0 output                                                                                                                                                             |

| 19  | 15  | _                                  |                                 | PWM0 output QC Port Group 1: plus-end input                                                                                                                             |

| 19  | 15  | PWM0                               | O<br>AI<br>AO                   | PWM0 output                                                                                                                                                             |

| 19  | 15  | PWM0<br>DP1                        | O<br>AI                         | PWM0 output  QC Port Group 1: plus-end input  QCDP1 VREF voltage output                                                                                                 |

|     |     | PWM0 DP1 QCDP1_VREF                | O<br>AI<br>AO                   | PWM0 output  QC Port Group 1: plus-end input  QCDP1 VREF voltage output  Reset pin input, with a 40K pull-up resistor by defau                                          |

|     |     | PWM0 DP1 QCDP1_VREF NRST           | O<br>AI<br>AO<br>I              | PWM0 output  QC Port Group 1: plus-end input  QCDP1 VREF voltage output  Reset pin input, with a 40K pull-up resistor by defau  Universal input/output pin              |

| 20  | 16  | PWM0 DP1 QCDP1 VREF NRST PA6 AINP3 | O<br>AI<br>AO<br>I<br>I/O<br>AI | PWM0 output  QC Port Group 1: plus-end input  QCDP1 VREF voltage output  Reset pin input, with a 40K pull-up resistor by defau  Universal input/output pin  AINP3 input |

|     |     | PWM0 DP1 QCDP1_VREF NRST PA6       | O AI AO I I I/O                 | PWM0 output  QC Port Group 1: plus-end input  QCDP1 VREF voltage output  Reset pin input, with a 40K pull-up resistor by defau  Universal input/output pin              |

|    | i  |                 |          | ř.·                                                                                  |

|----|----|-----------------|----------|--------------------------------------------------------------------------------------|

|    |    | DM0             | AI       | QC Port Group 0: minus-end input                                                     |

|    |    | QCDM0_VREF      | AO       | QCDM0_VREF voltage output                                                            |

|    |    | PA7             | I/O      | Universal input/output pin                                                           |

|    |    | AINN3           | AI       | AINN3 input                                                                          |

|    |    | UART0_TXD       | О        | UART0 clock signal                                                                   |

|    |    | SPI0 MOSI       | I/O      | SPI0 master output/slave input signals                                               |

|    |    | PWM1            | О        | PWM1 output                                                                          |

| 22 | 18 |                 |          | Waking up pins under power down mode. Effective                                      |

|    |    | WKUP0           | I        | under high level.                                                                    |

|    |    | STADC           | I        | ADC Trigger Input Pin                                                                |

|    |    | C0N             | AI       | Minus-end input of Comparator 0                                                      |

|    |    | DP0             | AI       | QC Port Group 0: plus-end input                                                      |

|    |    | QCDP0 VREF      | AO       | QCDP0 VREF voltage output                                                            |

|    |    | PB0             | I/O      | Universal input/output pin                                                           |

|    |    | AINP4           | AI       | AINP4 input                                                                          |

|    |    | COP             | AI       | Plus-end input of Comparator 0                                                       |

| 23 |    | TM TRG1         | I        | Timer External Trigger Input 1                                                       |

|    |    | PWM0            | 0        | PWM0 output                                                                          |

|    |    | PWM0L           | 0        | Complementary PWM0L output                                                           |

|    |    | PB1             | I/O      | Universal input/output pin                                                           |

|    |    | AINN4           | AI       | AINN4 input                                                                          |

| 24 |    | PWM1            | 0        | PWM1 output                                                                          |

| 24 |    | PWM0H           | 0        | Complementary PWM0H output                                                           |

|    |    | PB7             | I/O      | Universal input/output pin                                                           |

| 25 |    | PWM2H           | 0        | Complementary PWM2H output                                                           |

| 23 |    | PB8             | I/O      | Universal input/output pin                                                           |

| 26 |    | PWM2L           | 0        | Complementary PWM2L output                                                           |

|    |    | PA8             | I/O      | Universal input/output pin                                                           |

|    |    | AINP5           | AI       | AINP5 input                                                                          |

|    |    | I2C0 SDA        | I/O      | I <sup>2</sup> C0 data signals                                                       |

|    |    | UARTO RXD       | I        | UART0 receipt signal                                                                 |

| 27 | 19 | SPIO SS         | I/O      | SPI0 chip select signals                                                             |

|    |    | PWM0            | O        | PWM0 output                                                                          |

|    |    | EINT2           | I        | EINT2 input                                                                          |

|    |    | T2              | I        | Timer 2 input                                                                        |

|    |    |                 |          | 1                                                                                    |

|    |    | PA9             | I/O      | Universal input/output pin                                                           |

| 20 | 20 | AINN5           | AI I/O   | AINN5 input                                                                          |

| 28 | 20 | I2C0_SCL        | I/O      | I <sup>2</sup> C0 clock signal                                                       |

|    |    | UARTO_TXD       | 0        | UART0 clock signal                                                                   |

|    |    | SPIO_MISO       | I/O      | SPI0 master input/slave output signals                                               |

|    |    | PA10            | I/O      | Universal input/output pin                                                           |

| 20 |    | AINP6           | AI       | AINP6 input                                                                          |

| 29 | 21 | COP             | AI       | Plus-end input of Comparator 0                                                       |

|    |    | PWM1            | 0        | PWM1 output                                                                          |

|    |    | PWM1L           | 0        | Complementary PWM1L output                                                           |

|    |    | PA11            | I/O      | Universal input/output pin                                                           |

|    |    | AINN6           | AI       | AINN6 input                                                                          |

| 30 | 22 | CON             | AI       | Minus-end input of Comparator 0                                                      |

|    |    | PWM2            | О        | PWM2 output                                                                          |

|    |    | PWM1H           | О        | Complementary PWM1H output                                                           |

|    |    | PB2             | I/O      | Universal input/open drain output pin                                                |

| 31 | 23 | PWM2            | О        | PWM2 output                                                                          |

|    |    |                 |          |                                                                                      |

| 32 | 24 | VBUS_EN2<br>PB3 | O<br>I/O | High voltage control switch, open drain output Universal input/open drain output pin |

|   |   | VBUS_EN1 | I/O | High voltage control switch, open drain output |

|---|---|----------|-----|------------------------------------------------|

|   |   | C1P      | AI  | Plus-end input of Comparator 1                 |

|   |   | CKO      | О   | Frequency divider output                       |

| _ | - | EPAD     | GND | Ground                                         |

# 3. Functional Description

### 3.1. MCU subsystem

The MCU subsystem features are stated in the following:

- The CS32G020/1 series are 32-bit microprocessors integrated with an ARM® Cortex<sup>TM</sup>-M0 core.

- Applicable to industrial control and occasions requiring high performance and low power consumption.

- The core contains a serial debugging interface (SWD) that can be used for development debugging and application programming.

- Supporting 4 breakpoints and 2 viewpoints.

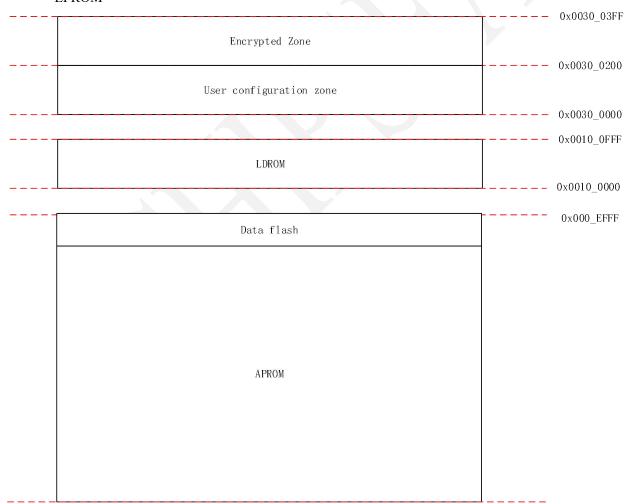

### 3.2. Flash

The CS32G020/1 is integrated with 60K on-chip Flash as application memory (APROM). The characteristics of the Flash controller are as follows:

- Zero latency continuation Flash read access of up to 24 MHz

- 60KB application memory space (APROM)

- 4KB BootLoader space (LDROM)

- Configurable data Flash, 512-byte page erase unit

- All built-in Flash page erase unit is 512 bytes

- Supporting in-system programming (ISP)/in-application programming (IAP) to update on-chip Flash EPROM

Figure 5 Block diagram of flash memory controller

### 3.2.1. LDROM

LDROM is used to store BootLoader. The space for BootLoader in CS32G020/1 is 4K bytes. Users can't modify any program in LDROM.

## 3.3. User configuration zone

User configuration zone is an internally programmable configuration zone. There are a total of 4 addresses for user configuration zone in flash memory, i.e.  $0x0030\_0000$ ,  $0x0030\_0004$ ,  $0x0030\_0008$  and  $0x0030\_000C$ . Its content is used to configure certain external registers during system startup. The lower half-word is user configuration bits, while the higher one is the negation of the user configuration bits.

Table 3 CONFIG0 (address =  $0x0030\_0000$ )

| 31    |      | 30       | 29                                                                                                                                                                                                                                          | 28             | 27      | 26           | 25      | 24        |  |

|-------|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------|--------------|---------|-----------|--|

| ~CWD  | TEN  | ~CLIRC_E | N Res                                                                                                                                                                                                                                       | Reserve        |         | ~CDELAY[1:0] |         | ~HIRC_SEL |  |

| 23    |      | 22       | 21                                                                                                                                                                                                                                          | 20             | 19      | 18           | 17      | 16        |  |

| ~CBOI | DEN  |          | ~CBOV[2:0]                                                                                                                                                                                                                                  |                | ~CBORST | ~CHVR<br>ST  | Reserve | Reserve   |  |

| 15    |      | 14       | 13                                                                                                                                                                                                                                          | 12             | 11      | 10           | 9       | 8         |  |

| CWDT  | EN   | CLIRC_E  | N Res                                                                                                                                                                                                                                       | erve           | CDELA   | Y[1:0]       | XT_SEL  | HIRC_SEL  |  |

| 7     |      | 6        | 5                                                                                                                                                                                                                                           | 4              | 3       | 2            | 1       | 0         |  |

| CBOD  | EN   |          | CBOV[2:0]                                                                                                                                                                                                                                   |                | CBORST  | CHVRS<br>T   | Reserve | Reserve   |  |

| Bits  |      |          |                                                                                                                                                                                                                                             | Desci          | ription |              |         |           |  |

| 31:16 | Rese | rve      | Inverse code of the                                                                                                                                                                                                                         | ne lower 16 bi | ts      |              |         |           |  |

| 15    | CWI  | OTEN     | Watchdog enabl<br>0 = Enabling watchdog<br>1 = The watchdog                                                                                                                                                                                 | chdog timer w  |         |              |         |           |  |

| 14    | CLII | RC_EN    | LIRC enable control  0 = Forcing the 10K clock source of LIRC to be constantly enabled and cannot be disabled by software.  1 = The 10K clock source of LIRC is controlled by LIRC EN (CLKCON[3]).                                          |                |         |              |         |           |  |

| 13:12 | Rese | rve      | Reserve                                                                                                                                                                                                                                     |                |         |              |         |           |  |

| 11:10 | CDE  | LAY[1:0] | Selection of reset delay  00 = 20ms 01 = 40ms 10 = 60ms 11 = 98ms CDELAY[1:0] is the bit for delay selection, and valid when the delay selection is opposite to parity bit. For other conditions, the max. delay of 98 ms is also selected. |                |         |              |         |           |  |

| 9     | Rese | rve      | Reserve                                                                                                                                                                                                                                     |                |         |              |         |           |  |

| 8     | HIR  | C_SEL    | Frequency selection of built-in high-speed oscillator  1 = 24MHz 0 = 8MHz                                                                                                                                                                   |                |         |              |         |           |  |

| 7     | СВС  | DDEN     | Undervoltage detection enablement  0 = Enabling undervoltage detection when powered on  1 = Disabling undervoltage detection when powered on  Note: Enabling/disabling undervoltage detection will enable/disable 6.5 V high                |                |         |              |         |           |  |

| 6:4   | СВС  | 0V[2:0]  | voltage detection simultaneously.  Selection of undervoltage value  000 = 1.8V  001 = 2.0V  010 = 2.4V  011 = 2.7V                                                                                                                          |                |         |              |         |           |  |

|     |         | 100 = 3.0 V                                            |

|-----|---------|--------------------------------------------------------|

|     |         | 101 = 3.6V                                             |

|     |         | 110 = 4.0V                                             |

|     |         | 111 = 4.0V                                             |

|     |         | Enablement of undervoltage reset                       |

| 3   | CBORST  | 0 = Enabling undervoltage reset when powered on        |

|     |         | 1 = Disabling undervoltage reset when powered on       |

|     |         | Enablement of 6.5 V high voltage reset                 |

| 2   | CHVRST  | 0 = Enabling 6.5 V high voltage reset when powered on  |

|     |         | 1 = Disabling 6.5 V high voltage reset when powered on |

| 1:0 | Reserve | Reserve                                                |

# **Table 4 CONFIG1 (address = 0x0030\_0004)**

| 1     |                |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                |                |                |      |           |       |  |

|-------|----------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------|----------------|------|-----------|-------|--|

| 31    | 31 30          |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29 28 2                        |                |                | 26   | 25        | 24    |  |

| ~CWDT | WDTSEN Reserve |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ~!                             | CWDTSIS[2:0    | 0]             |      | ~FRD CFG[ | 2:0]  |  |

| 23 22 |                |            | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20                             | 19             | 18             | 17   | 16        |       |  |

|       | ~CE            | BS[1:0]    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                |                | Reserve        |      |           | ~DFEN |  |

| 15    |                | 14         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13                             | 12             | 11             | 10   | 9         | 8     |  |

| CWDT  | SEN            | Reserve    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (                              | CWDTSIS[2:0    | ·]             |      | FRD CFG[2 | 2:0]  |  |

| 7     |                | 6          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                              | 4              | 3              | 2    | 1         | 0     |  |

|       | СВ             | S[1:0]     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                |                | Reserve        |      |           | DFEN  |  |

| Bits  |                |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                | Desci          | ription        |      |           |       |  |

| 31:16 | Rese           | rve        | Inv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | erse code of th                | ne lower 16 bi | ts             |      |           |       |  |